Intel apresenta chips com novo material e wafers mais eficientes

A Intel revelou no IEDM 2024 novas tecnologias para seus próximos chips. O destaque fica para um novo método de realizar interconexões nos semicondutores por meio de rutênio subtrativo e soluções de wafers ultrafinos.

O rutênio subtrativo é encontrado em minas de platina e é usado para reforçar ligas metálicas. A empresa diz que utilizará lacunas de ar e sua alta resistividade para reduzir em até 25% a capacidade de armazenamento elétrico linha a linha nos chips.

A adoção do rutênio também é uma forma de substituir o cobre de damasceno utilizado atualmente nas conexões entre o silício. Segundo a empresa, o novo método não requer litografias mais caras e se trata de um processo “integrado, prático, econômico e compatível com fabricação em larga escala”.

Wafers ultrafinos

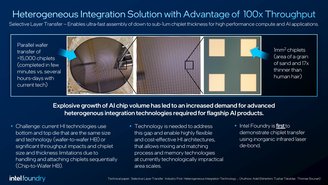

O evento também revelou melhorias na produção massiva dos wafers de silício usados pela divisão de fabricação da Intel. A novidade é o Selective Layer Transfer (SLT), ou seja, uma tecnologia que permite o desenvolvimento de wafers ultrafinos, resultando em chips cada vez menores.

A ideia do novo procedimento é que esses pacotes tenham mais densidade funcional e um manuseio mais flexível, já que os wafers são conhecidos por serem extremamente frágeis. Dessa forma, a expectativa da companhia é que a taxa de transferência chip a chip seja até 100 vezes mais veloz.

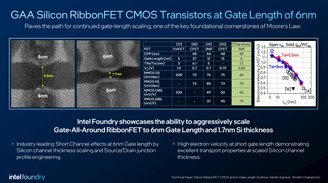

Avanços em RibbonFET GAA

Durante a apresentação, a Intel Foundry destacou bastante as inovações quando o assunto são transistores GAA (Gate-all-arround). Um exemplo são os novos transistores CMOS (Semicondutor de Óxido Metálico Complementar) RibbonFET de apenas 6 nanômetros, que tiveram reduções expressivas no tamanho dos canais para chegar a esse tamanho.

Vale lembrar que as tecnologias RibbonFET serão usadas diretamente no processo de fabricação 18A, da ordem de 1,8 nm. Para complementar esse tipo de tecnologia, a companhia também anunciou transistores NMOS e PMOS com GAA 2D, que utilizam dicalcogeneto de metal de transição como um possível substituto para o silício em processos avançados dessa categoria.

Por enquanto, esses transistores estão apenas em fase de pesquisa e devem demorar a serem incorporados nos produtos da empresa. Além dos anúncios no IEDM 2024, a Intel deve aparecer na CES 2025, em janeiro, com novos produtos voltados ao mercado doméstico.